Gen6 PCIe/CXL 2x8 to 2x8 Retimer

Product Description

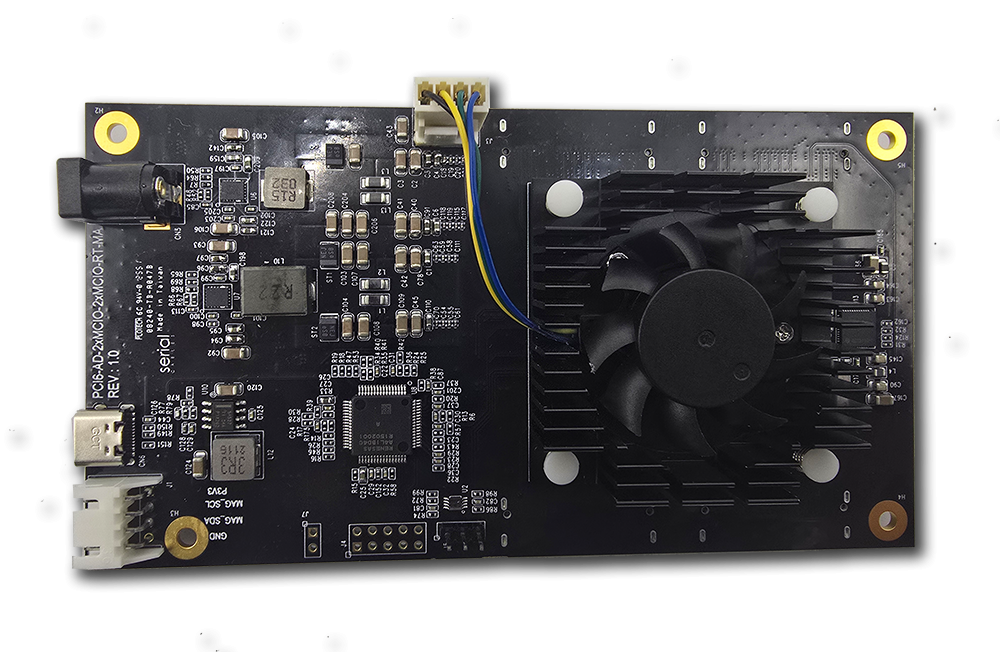

PCI6-AD-2xMCIO-2xMCIO-RT — PCIe/CXL Gen6 Retimer Card

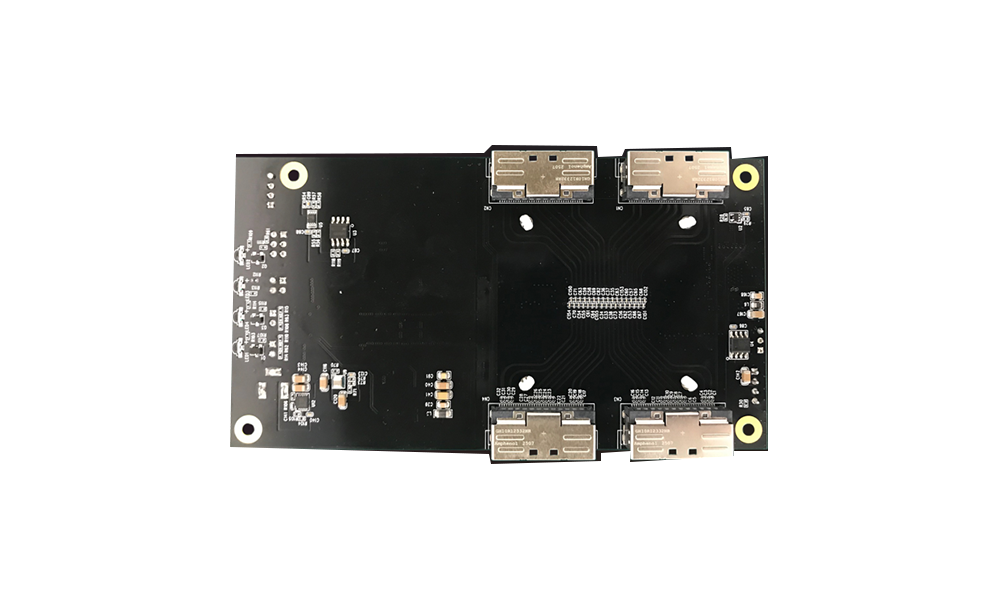

The Serial Cables PCI6-AD-2xMCIO-2xMCIO-RT is a PCIe/CXL Gen6 active retimer card designed to extend signal reach in high-speed interconnect validation and deployment environments. Featuring four MCIO SFF-TA-1016 connectors in a compact 76 × 140 × 24mm form factor, the card provides two x8 root-side and two x8 endpoint-side ports, supporting full x16 link configurations as well as bifurcated x8, x4, and x2 lane groupings.

Available with either the Marvell Alaska P, Credo Toucan or Broadcom Vantage 16-lane Gen6 retimer IC, the card supports PCIe Gen1 through Gen6 (64 GT/s) and CXL 3.1, extending channel reach beyond 36 dB at full line rate. The integrated active fan-sink provides thermal management for continuous operation with no software or driver installation required.

Powered via a standard 12V DC jack, the card exposes an SMBus interface header (J1) for optional retimer IC and EEPROM access, making it well-suited for signal integrity validation, cable reach characterization, and system bring-up testing.

Key Specs:

- Retimer IC: Credo Toucan or Marvell Alaska P (16-lane Gen6) or Broadcom (16-lane Gen6)

- Connectors: 4× MCIO x8 (2× Root / 2× Endpoint)

- Protocols: PCIe Gen1–Gen6, CXL 3.1

- Power: 12V DC, max ~10W

- Dimensions: 76 × 140 × 24mm

- No driver/software required

| User's Manual | Download |

Retimer IC — Marvell Alaska® P (MV-CHP10160)

The MV-CHP10160 exceeds PCI-SIG electrical specifications, supporting greater than 32 dB insertion loss at 64 GT/s (PCIe 6) and greater than 36 dB insertion loss at 32 GT/s (PCIe 5) at 16 GHz Nyquist frequency. Advanced equalization features accommodate various channel topologies, and the device achieves a First Bit Error Rate (FBER) better than 1E−6.

The retimer follows the Intel PCIe 6.0 Retimer Supplemental Footprint for generation-to-generation design compatibility. It is manufactured on an advanced process node and delivers significant power efficiency. Device configuration is supported through SMBus/I³C, EEPROM, or SPI Flash. Integrated diagnostics include on-chip voltage and thermal sensors, an embedded logic analyzer with history FIFO, GPIO status indicators, and IEEE 1149.6 AC-JTAG boundary scan.

|

Feature |

Detail |

|

Standards & Compatibility |

|

|

PCIe Compliance |

PCI Express Gen 6.x / 5 / 4 / 3 / 2 / 1 |

|

CXL Compliance |

CXL 3.x / 2.0 / 1.1 (low-latency cache-coherent mode) |

|

Data Rates |

64 GT/s, 32 GT/s, 16 GT/s, 8 GT/s, 5 GT/s, 2.5 GT/s |

|

Encoding |

PAM4 (Gen6/5) and NRZ (Gen4 and below) |

|

Lane Count |

32 bi-directional (16 upstream + 16 downstream) |

|

Link Bifurcation |

1×16, 2×8, 4×4, 8×2, and additional combinations |

|

Hot Plug |

PCIe hot-add and hot-removal per link/partition |

|

Footprint Compatibility |

Intel PCIe 6.0 Retimer Supplemental Footprint |

|

I/O Performance |

|

|

Insertion Loss (PCIe 6) |

> 32 dB at 64 GT/s (16 GHz Nyquist) |

|

Insertion Loss (PCIe 5) |

> 36 dB at 32 GT/s (16 GHz Nyquist) |

|

FBER |

Better than 1E−6 |

|

Equalization |

Advanced CTLE + DFE + TX FIR; multi-topology support |

|

Clocking |

|

|

Clock Input |

PCIe base-spec compliant 100 MHz reference clock |

|

Clock Output |

HCSL reference clock output to downstream devices |

|

Clocking Modes |

Common Clock, SRIS, and SRNS |

|

Management, Debug & Diagnostics |

|

|

Management Interface |

I²C / SMBus with I³C extensions |

|

Configuration |

SMBus/I³C, EEPROM, or SPI Flash |

|

Sensors |

On-chip voltage and thermal monitoring |

|

Diagnostics |

Embedded logic analyzer, history FIFO, advanced telemetry |

|

GPIO |

Link status and functional status indication |

|

Boundary Scan |

IEEE 1149.6 AC-JTAG |

|

Package |

|

|

IC Package |

8.9 mm × 22.8 mm HFETBGA, 0.5 mm minimum ball pitch |

|

Power Rails |

Three external power rails |

|

DC-Blocking Caps |

Package options for integrated DC-blocking capacitors |

|

Simulation Support |

IBIS-AMI model available |